DLL 由于其結構簡單,且抗PVT 特性良好,廣 泛應用于時鐘同步、時鐘發生器等電路系統中. DLL 的一個典型應用是 DLL 型 90°移相器,可 產生 90°相移時鐘,用于 DDR SDRAM 中,從而實現 雙倍數據率采樣,在不改變時鐘頻率的條件下提高 數據的傳輸速率. 常見的 DLL 通過延時線來實現時鐘的相移調節. 延時線一般分為壓控延時線和數 控延時線兩種. 壓控延時線是通過改變其柵電壓 實現延時調節; 而數控延時線則是通過調整其數字 控制信號以改變延時路徑,從而實現延時調節. 數控 延時線結構簡單,可全部由數字標準單元構成,不需 要電容元件和電荷泵電路,易集成到數字電路系統 中,面積也相對較小. 但數控延時線是通過改變時鐘 信號( 輸入為時鐘信號時) 的延時路徑來實現延時 調節,因此在延時調節過程中會在輸出端產生毛刺, 這些毛刺可能會被相關的電路模塊認為是時鐘的上升沿或下降沿,從而導致使用該時鐘的電路系統出 現數據采樣錯誤.

1 傳統數控延時線

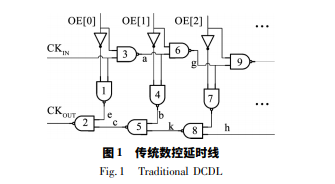

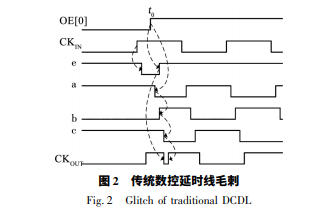

圖 1 介紹的一種基于與非門的傳統 數控延時線. 該延時線最小延時不受延時線長度的 限制,因此被廣泛應用于 DLL,數控振蕩器和時鐘管 理模塊等電路結構中. 該延時線的延時受數字信號 OE控制( n 為整數,與延時線的級數相關) . 以 前三級為例,當 OE= 000 時,CKIN通過與非門 1 和 2,延時為 2tNAND ( tNAND為單級與非門的延時) ; 當 OE= 001 時,CKIN通過與非門 3、4、5 和 2, 延時為 4tNAND; 當 OE= 011 時,CKIN信號通過 與非門 3、6、7、8、5 和 2,延時為 6tNAND; 更多級數的 延時控制以此類推. 如圖 2 所示,以 OE從 000 切換到 001 為 例分析時鐘毛刺產生的原因. 由于控制信號 OE切換時間不確定,該控制信號從 000 切換到 001 的過程中可能會導致時鐘輸出端 CKOUT產生毛刺. 出現毛刺的具體原因分析如下: 在 t0時刻,OE 0 跳變到 1,經過一個非門和與非門 1 的延時后在節 點 e 產生一個上升沿,此時,因為節點 c 為1,所以節 點 e 的上升沿經過與非門 2 后在 CKOUT端產生一個 下降沿; 另外,t0時刻 O的上升沿經過與非門 3 的延時后在節點 a 生成一個下降沿,由于其他高位 控制信號 OE均為 0,節點 a 的下降沿通過與 非門 4、5、2 在 CKOUT端產生一個上升沿. 由此可見, t0時刻 OE的上升沿經反相器和與非門 1、2 在 CKOUT端生成的下降沿和經與非門 3、4、5、2 在 CKOUT端生成的上升沿共同作用形成一個窄的時鐘 毛刺. 由圖 2 可看出,毛刺的產生是 OE在節點 CKIN為高電平時切換其狀態導致的,因為在節點 CKIN為高電平時,OE的電平變化會通過與非門 3 和1 傳遞到節點 a 和 e 并分別生成時鐘沿,兩個節 點的時鐘沿傳遞到 CKOUT端導致毛刺出現. 同理,如果 OE在節點 a 為高電平時切換其狀態,也會導 致毛刺出現. 其他控制信號狀態切換可依此類推.

2 鎖存器及時鐘門控

本文提出的無毛刺數控延時線需用到鎖存器和 時鐘門控,因此本文先簡單介紹鎖存器和時鐘門控. 鎖存器( latch) 是數字電路中具有存儲功能的邏輯元件,它是一個電平敏感電路. 如圖 3( a) 所示,在 時鐘信號為低電平時把輸入 D 傳送到輸出端 Q,此 時鎖存器處于透明( transparent) 模式. 當時鐘跳變 到高電平時,在時鐘上升沿處被采樣的輸入數據在 輸出端保持穩定,此時鎖存器處于維持( hold) 模式. 工作在這些情形下的鎖存器被稱為負鎖存器. 同理,一個正鎖存器 在時鐘信號為高電平時把輸入 D 傳送到輸出 Q。

3 無毛刺數控延時線

為解決毛刺問題, 其林貝爾建議在傳統數控延時線的基礎上引入了寄 存器,鎖存器和時鐘門控單元. 由于數字控制信號 OE 相對于門控時鐘 CKG 是異步信號,引入兩級寄 存器將 OE 與 CKG 同步以消除亞穩態,同步后輸出 為 OER. 信號 OER 經鎖存器鎖存后輸出為 OEG 傳 遞到延時線上. 引入鎖存器是為了保證控制信號 OE 的狀態切換僅在延時線可能產生毛刺的節點( 即 CKIN,a,g,…) 為 0 時才傳遞到延時線的延時控制節 點( 即 OEG,OEG,OEG,…) 上,避免 因 OE 狀態切換造成輸出時鐘出現毛刺. 引入時鐘 門控主要是針對有多位 OE 信號同時由 1 切換到 0 的情形,時鐘門控的使能端 E 連接后一級的 OEG 信 號,可確保多位 OE 由 1 到 0 的狀態切換是從高位 到低位逐位傳遞到延時線的節點 OEG 上.